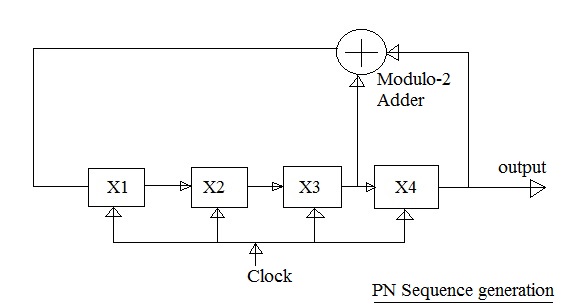

Spread the bandwidth of baseband modulated signal to the much larger bandwidth before transmission to distiguish between different users by allocating unique PN sequences to them. LFSR Linear Feedback Shift Register is commonly employed in various cryptography applications to generate pseudo-random numbers.

Pn Sequence Code Generator Download Scientific Diagram

The prototype can also be extended to generate any of the desired sequence of length of 8 bit by extending the circuit.

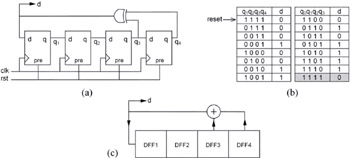

. Here in this article we deal with the designing of sequence generator using D flip-flops please note that even JK flip-flops can be made use of. Where h can be either 1 short circuit or 0 open circuit and xs are the shift registers. How to generate a PN sequence in LABVIEW.

The Sequence Generator block is designed to operate in two. Since the circuit itself must self generate the next number in the sequence the design must be able to hold the first two starting numbers in the. PN pseudorandom sequence generates a sequence of pseudorandom binary numbers.

Lets take an example that we aim to design a circuit that moves throughout the states of 0-1-3-2 before doing again the similar pattern. At each clock pulse the data in the registers will right shift once and one. Darshil shah I1241090051 2.

Sequence Generator Digital Circuits FSM K-map simplification. Properties of PN sequence. It can also be used in spread-spectrum system.

OUTLINE What is PN code. A 15-stage PN generator. The following is the description of this process.

I This implies that. Simple Pseudo Random Number Generator with complete sequence. Because the recursive circuit has no perturbing input only initial states and is marginally.

The circuit includes 8 single-way micro switches and a parallel to serial convertor. If S1S0 00 then the current value is locked to the next state. F knowledge of andemodulationpossible F without knowledge of fangdemodvery di cult I If fangie.

Since the PN sequence is generated by a digital circuit called the PN generator it is a completely deterministic binary sequence 0 1. Flexible Pulse Sequence Generator. PN generator produces periodic sequence that appears to be random Generated by an algorithm using initial seed Sequence isnt statistically random but will pass many test of randomness Sequences referred to as pseudorandom numbers or pseudo.

This paper proposes a very simple chaotic circuit which contains a charge-controlled memristor a capacitor and an inductor for generating pseudo random PN sequences. The steps involved during this process are as follows. Pseudorandom Noise SequencePN sequence Basics.

MAT-Lab Simulation for PN sequence generation. However LFSR circuits are implemented with VLSI technology and a PN sequence generator design may vary in respect to power dissipation area and propagation delay. A PN data sequence is an M-sequence that is generated using a linear feedback shift-register circuit as illustrated below.

The circuit can exhibit chaos in appropriate parameters of capacitance and inductance. Application of PN sequence. Clock Generation Circuit with NE555 Timer.

PN Sequence Presented By. The circuit also needed to support an enable input signal which would control if the circuit should advance and calculate the next number in the sequence or hold its previous value. fipasswordfl is purely random with no.

A pseudonoise sequence can be used in a pseudorandom scrambler and descrambler. What is PN code. This figure defines a PN sequence generator with a generator polynomial p z z 6 z 1 and a mask m z z 5 z 4 z 2 1.

PN sequence stands for Pseudorandom Noise Sequence. The shift register I need to use is the 74LS194 model shown below where the inputs S1 S0 controls the shift mode. The PN sequence is usually generated using sequential logic circuits.

Data detection by correlation with PN code. Design and Simulation of 4 bit PN Sequence Generator 4 bit PN sequence generator can be built with LFSR. D M is the m th shift register and c1c2cM are the coefficients of them.

The Digital Sequence Generator top-level design contains several macros whose sequential interaction produces the desired output. Study Verilog Implementation of PN Sequence generator using Fibonacci and Galois method. Parallel to serial conversion can be done by using IC 74165.

The example shows a few of the formatting options available to define the generator. You can generate PN sequence by using shift registers see the diagram. As an example let us consider that we intend to design a circuit which moves through the states 0-1-3-2 before repeating the same pattern.

Binary sequences are shifted through the shift registers in response to clock pulses and the output of the various stages are logically. 11 6Further Extension. 1 65535 PN sequence.

M is the number of shift registers. Implementation Of PN Sequence Using Vedic Mathematics The two message bits are X and Y are multiplied using vedic and then using the string of multiplied result are masked to generate PN sequence Using modulo -2 operator. Fig35 The block diagram of 16 bit LFSR 4.

PN sequence is widely used in CDMA systems for the following reasons. Design of PN sequence generator based on memristor oscillator. If helps press helped me.

A feedback shift register which is shown in figure 111 consists of consecutive stages of two state memory devices and feedback locig. Example of PN sequence 3. Refer to the figure A3 in Appendix A for detailed view of the Sequence Generator top-level schematic.

The Circuit diagram is shown. Here we are designing a sequence generator using D FFs in different steps. Harshita Kumar PN Sequences.

The block diagram of 16 bit LFSR is shown in Figure 35. The overall number of random state produced by the LFSR is determined by the. The PN generator circuit comprises a solitary binary register as would be found in almost every microprocessor.

How can I implement a sequence generator that generates the following sequence 0000 1000 0001 0011 0110 1101 1110 1111 using a universal shift register. When configuring a PN sequence generator System object you have options regarding how to express the polynomial and the mask. Circuit diagram of pn sequence generator.

Introduction Denition of a SSS The PN signal bt is a function of a PN sequence of 1s fang I The sequences fangmust agreed upon in advance by Tx and Rx and they have status of password. Thus in CDMA systems a careful. This paper implements 8 16 and 32 bit LFSR for PN sequence generation using VHDL to study its performance and analyse the behaviour of its randomness.

Similarly there are different steps involved in designing a sequence generator using JK Flip-Flops.

Sequence Generator Electrical4u

Db20 Pn Sequence Generator Experiment Board And Trainer Kit With 1 Year Warranty Amazon In Industrial Scientific

Block Diagram Of Pn Sequence Generator 3 1 3 Bpsk Modulator The Spread Download Scientific Diagram

Block Diagram Of Pn Sequence Generator 3 1 3 Bpsk Modulator The Spread Download Scientific Diagram

How Is A Pn Sequence Generated Quora

Pn Sequence Generator Forum For Electronics

0 comments

Post a Comment